Серия программируемых СнК с обширными возможностями настройки

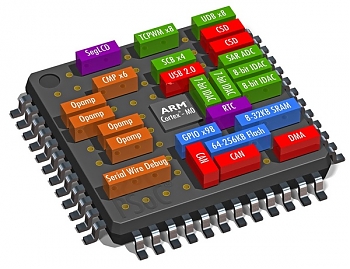

Компания Cypress Semiconductor представила новейшую серию компонентов PSoC 4 L-series, вошедших в семейство программируемых систем-на-кристалле (СнК). Новые компоненты, основанные на широко распространённой архитектуре ARM M0, обеспечивают богатыми возможностями настройки.

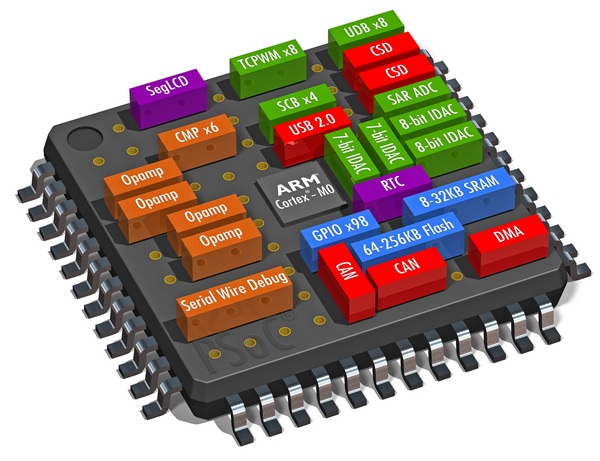

Набор фиксированных ресурсов в чипах PSoC-4 серии L включает, к примеру, 98 входов/выходов GPIO, контроллер USB-устройств, DMA-контроллер, контроллер ЖК-дисплея, интерфейс CAN. Также реализован контроллер сенсорных экранов (с поддержкой взаимной ёмкости) с 94 каналами. Для кастомизации чипов предусмотрено 33 программируемых блока, работающих как с аналоговыми, так и цифровыми ресурсами.

Двадцать цифровых блоков выполнены в виде трёх вариантов: блоки счётчик/таймер/ШИМ, блоки последовательного взаимодействия и так называемые универсальные цифровые блоки (UDB). Блок счётчик/таймер/ШИМ может работать в любой из трёх функций и имеет разрядность 16 бит. Блоки последовательного взаимодействия могут быть настроены как интерфейсы I2C, SPI или UART, а также EZI2C, имитирующий интерфейс EEPROM.

Универсальные блоки UDB имеют несколько более сложный механизм. Они состоят из двух программируемых логических устройств с настраиваемыми каналами данных, статуса и управляющих регистров. Каналы могут сочетаться различным образом, формируя разнообразную 16- и 32-разрядную логику. Это позволяет создавать автоматы состояний, реализовывать стыковочную логику, сопроцессоры и заказную периферию.

Аналоговая часть включает операционные усилители, блоки ЦАП, компараторы и 12-разрядный SAR АЦП. Данные элементы можно связывать между собой, настраивать уровни усиления, формировать блоки сопряжения для работы с датчиками. Для упрощения компоновки предусмотрена настраиваемая распиновка.

Cypress предлагает специальный инструмент разработки PSoC Creator, позволяющий выполнить настройку в несколько кликов мыши. Часто используемые конфигурации доступны в библиотеках в качестве виртуальных чипов, а собственные конфигурации создаются при помощи ввода описания схем либо при помощи языка Verilog.

Подписаться на почтовую рассылку / Авторам сотрудничество