Повышение энергоэффективности: ключевой аспект будущего проектирования SoC

За последние четыре десятилетия полупроводниковая индустрия сделала огромные шаги вперед, двигаясь от простых микроэлектронных схем к высокопроизводительным вычислительным системам, которые могут выполнять квинтиллионы операций в секунду (эксаскейл).

Этот прогресс был достигнут благодаря многочисленным инновациям в области архитектуры процессоров, разработке более емкой и быстрой памяти, а также улучшению технологий межсоединений, которые обеспечивают эффективную передачу данных между различными компонентами системы на кристалле (SoC). Однако текущее развитие столкнулось с серьёзными проблемами из-за приближения к фундаментальным физическим ограничениям кремниевых транзисторов, основанных на технологии комплементарных металлооксидных полупроводников (КМОП или CMOS).

КМОП-технология, которая десятилетиями лежала в основе микроэлектроники, достигла своего предела масштабирования, поскольку дальнейшее уменьшение размеров транзисторов становится технически сложным и экономически нецелесообразным. Это связано как с проблемами литографии — методов, используемых для создания нанометровых элементов на чипах, так и с физическими ограничениями самих транзисторов, такими как утечки тока и увеличение сопротивления межсоединений при уменьшении их размеров.

Вдобавок к этому, экономические аспекты также играют свою роль: увеличение размеров кристаллов (чипов) за пределы допустимого размера фотошаблона (826 мм²) ведет к значительному удорожанию производства. В этих условиях традиционные подходы к масштабированию производительности становятся всё менее эффективными, что требует разработки новых стратегий проектирования и производства систем на кристалле.

Одной из ключевых проблем будущего является не только увеличение вычислительной мощности, но и улучшение энергоэффективности, поскольку дальнейший рост вычислительных возможностей неизбежно приведет к огромному увеличению энергопотребления. Например, системы эксаскейл уровня уже потребляют сотни мегаватт, а ожидаемые в будущем зетаскейл-системы, которые будут в 1000 раз мощнее, могут потреблять до 500 мегаватт — это сравнимо с половиной мощности ядерного реактора. Становится очевидным, что без значительных инноваций в проектировании энергоэффективных систем дальнейший прогресс будет ограничен не только техническими, но и экологическими и экономическими факторами.

Для решения этих задач потребуется комплексный подход, включающий разработку новых материалов, таких как транзисторы на основе двухмерных полупроводников (например, графен или дисульфид молибдена), переход на новые вычислительные парадигмы (например, квантовые или нейроморфные вычисления), а также внедрение более эффективных архитектур на уровне чипов.

Кроме того, уменьшение энергопотребления межсоединений, улучшение способов охлаждения и управление тепловыми потоками также станут критически важными элементами будущих SoC. Таким образом, будущее полупроводниковой индустрии будет зависеть не только от дальнейшего увеличения мощности, но и от умения сохранять эту мощность в пределах допустимого энергопотребления, обеспечивая при этом высокую производительность.

Эволюция масштабирования КМОП

Масштабирование КМОП долгое время было основой для увеличения вычислительной мощности, главным образом за счёт миниатюризации транзисторов, что соответствовало закону Мура. Уменьшение размеров транзисторов позволяло размещать больше функций на одном кристалле, повышая производительность, улучшая энергоэффективность и снижая производственные затраты. На ранних этапах уменьшение размеров транзисторов также повышало скорость, что дополнительно увеличивало вычислительные возможности.

Однако с развитием технологий индустрия столкнулась с проблемой насыщения частот CPU. Это привело к появлению многоядерных процессоров, которые позволяли выполнять программы параллельно на нескольких потоках, максимизируя вычислительную мощность без необходимости увеличения тактовых частот. Многоядерные архитектуры стали важным решением для увеличения производительности в условиях, когда дальнейшее повышение частоты процессоров стало невозможным.

Роль ИИ и тенденции энергоэффективности

Искусственный интеллект (ИИ) стал ключевым двигателем недавних достижений в вычислительной технике, особенно с ростом распределённых вычислений и приложений ИИ, таких как большие языковые модели (LLM). Современные графические процессоры (GPU), достигающие 4 TOPS/Вт, и тензорные процессоры (TPU), достигающие более 2 TOPS/Вт в серверных фермах, вывели производительность на новый уровень. Сегодняшние эксаскейл-серверы потребляют до 21 МВт, обеспечивая энергоэффективность на уровне 52 ГФ/Вт.

Несмотря на эти успехи, улучшение энергоэффективности отстаёт от роста производительности. За последние два десятилетия производительность удваивалась каждые 1,2 года, в то время как энергоэффективность — лишь каждые 2,2 года. Если эта тенденция сохранится, то через десятилетие при энергоэффективности в 2140 ГФ/Вт всё равно потребуется неустойчивые 500 МВт для достижения производительности зетаскейл-системы. Этот разрыв между ростом производительности и эффективностью подчёркивает необходимость изменения философии проектирования.

Ключевые направления для повышения энергоэффективности

Чтобы справиться с этими вызовами и достичь устойчивой энергоэффективности в будущем проектировании SoC, лидеры отрасли сосредотачиваются на трёх ключевых направлениях.

Новые архитектуры процессоров:

- Оптимизированные гибридные процессоры: Разработка гибридных процессоров, сочетающих сильные стороны CPU и GPU, может оптимизировать производительность для конкретных задач. Гибридные архитектуры, использующие преимущества обоих типов процессоров, могут улучшить общую энергоэффективность.

- Архитектуры, ориентированные на ИИ: Поскольку рабочие нагрузки ИИ всё больше ориентированы на обработку данных, создание архитектур, специально разработанных для ИИ-приложений, поможет эффективнее управлять обработкой данных, сокращая энергопотребление.

Приближение памяти к вычислительным блокам и кэширование

Приближение памяти к вычислительным блокам: Размещение памяти ближе к вычислительным элементам снижает затраты энергии на перемещение данных, что является значительным фактором потребления энергии в системах высокопроизводительных вычислений. Этот подход помогает минимизировать задержки и потери энергии, делая системы более эффективными.

Снижение накладных расходов на коммуникации

- Инновационный дизайн системы: Сокращение накладных расходов на коммуникации в дизайне SoC может оптимизировать процессы передачи данных, снижая энергозатраты и улучшая производительность системы. Оптимизация передачи данных внутри системы может значительно повысить энергоэффективность.

- Эффективные протоколы связи: Разработка более эффективных протоколов связи как на уровне чипа, так и за его пределами может обеспечить быструю и надёжную передачу данных между компонентами системы, что дополнительно снизит энергопотребление, связанное с передачей данных.

С ростом физических и экономических барьеров для масштабирования КМОП повышение энергоэффективности в проектировании SoC стало критически важной задачей. Разработка зетаскейл-систем потребует инновационных решений в архитектуре процессоров, расположении памяти и коммуникационных системах для эффективного управления энергопотреблением. Сосредоточив усилия на энергоэффективных дизайнах, полупроводниковая индустрия сможет продолжать улучшать производительность, обеспечивая при этом устойчивость будущих вычислительных систем.

Новые архитектуры процессоров: преодоление вызовов в ИИ и проектировании SoC

По мере того как модели ИИ продолжают стремительно расти, необходимость в инновационных архитектурах процессоров, интегрирующих быстрые и масштабные решения для хранения данных, становится всё более актуальной. Ведущие производители CPU и GPU используют свой опыт для разработки передовых аппаратных решений, которые включают различные типы памяти.

Ключевым технологическим сдвигом в этой эволюции является внедрение чиплетов — небольших частей кристаллов, объединённых в более мощный процессор. Этот дизайн позволяет преодолеть ограничения, накладываемые размером маски, которые ограничивают максимальные размеры кристаллов и влияют на выход годной продукции.

Технология чиплетов: ключевые преимущества:

- Гибкость продуктов: Чиплеты позволяют большую гибкость в проектировании многоядерных, масштабируемых CPU и GPU. Производители могут легко настраивать конфигурации для удовлетворения различных требований по производительности и стоимости, интегрируя разные чиплеты в одном корпусе.

- Повторное использование L3-кэша: Чиплеты позволяют повторно использовать крупные компоненты памяти, такие как кэш L3, оптимизируя производительность и эффективность CPU. Это достигается путём интеграции различных типов чиплетов в едином пакете.

- Экономичность: Одним из самых значительных преимуществ технологии чиплетов является её экономичность. В то время как процессорные ядра производятся с использованием передовых КМОП-технологий, компоненты памяти, такие как SRAM, изготавливаются с применением более зрелых технологий, что снижает общие производственные затраты.

Поскольку несколько чиплетов делят общий бюджет мощности, поддержание высокой энергоэффективности становится важным для размещения большего числа чиплетов в рамках тех же ограничений. Этот архитектурный сдвиг особенно важен для рабочих нагрузок ИИ, где традиционное оборудование сталкивается с проблемами, связанными с перемещением данных и энергопотреблением.

Инновационные решения для памяти для рабочих нагрузок ИИ

Стремительный рост ИИ и машинного обучения значительно увеличил спрос на память, что привело к изменениям в архитектуре процессоров. Чтобы преодолеть узкие места, связанные с перемещением данных, новые стартапы разрабатывают распределённые архитектуры, которые приближают память к ядрам процессора. Локальная распределённая память, в первую очередь SRAM, становится важной для повышения производительности ИИ-инференса.

Один из перспективных подходов включает 3D-складирование SRAM поверх логических CPU с использованием передовых технологий КМОП. Это позволяет разделить масштабирование SRAM и логики CMOS, оптимизируя производительность, мощность и стоимость. Однако добавление большего объёма SRAM увеличивает энергопотребление из-за утечек, что вызывает проблемы с теплоотводом. Следовательно, будущие SoC потребуют альтернативных решений для памяти, которые минимизируют утечки при сохранении производительности.

Архитектуры "вычисления в памяти" (CIM)

Для дальнейшего решения проблем с перемещением данных появились архитектуры вычислений в памяти (CIM). CIM интегрирует вычислительные возможности в память, сокращая узкие места передачи данных.

Исследователи изучают различные технологии энергонезависимой памяти, такие как фазопереходная память (PCM) и оксидно-резистивная память (OxRAM), чтобы внедрить аналоговые вычисления в памяти:

- PCM: Хранит данные путём изменения состояния материала с фазовым переходом между аморфным и кристаллическим состояниями. Однако она сталкивается с такими проблемами, как ограничение ресурса (ячейки выдерживают от 10^6 до 10^8 циклов), высокое энергопотребление и тепловое управление.

- OxRAM: Использует резистивное переключение в оксидах металлов для хранения данных, но такие проблемы, как изменчивость уровней сопротивления и долговечность данных, остаются серьёзными препятствиями.

Несмотря на эти достижения, GPU остаются доминирующим выбором для обучения и инференса ИИ. Однако энергозатраты при использовании GPU высоки: например, во время обучения GPT-4 было потреблено 10,8 ТВт·ч энергии при использовании 20 000 GPU A100 в течение 90-100 дней.

В то время как устройства на краю сети могут обрабатывать данные локально, делясь выводами с сетью для снижения энергопотребления, смартфоны и другие устройства сталкиваются с ограничениями по мощности из-за своих аккумуляторов, что требует энергоэффективных решений для памяти с низким энергопотреблением в режиме ожидания.

Приближение памяти и кэш

Кэш-память играет ключевую роль в современных вычислениях, устраняя разрыв между высокоскоростными CPU и медленной основной памятью. По мере того как рабочие нагрузки ИИ требуют всё большего объёма кэша, 6T SRAM, построенная с использованием КМОП-технологий, остаётся основным решением для приложений кэширования. Однако масштабирование SRAM сталкивается с серьёзными трудностями, создавая узкое место в доступности данных. Рынки серверов и SoC для ИИ теперь требуют кэш-памяти объёмом более 800 МБ для удовлетворения требований производительности.

Проблемы масштабирования SRAM:

- Стоимость: Масштабирование SRAM позволило добиться лишь 5%-ного сокращения площади с 5-нм FinFET до 3-нм, по сравнению с 28%-ным уменьшением площади логики CMOS, что приводит к высоким затратам на бит.

- Выход годной продукции и производительность: Проблемы, такие как ограничения литографии, паразитные эффекты металлов и физика транзисторов, отрицательно влияют на выход годной продукции и производительность SRAM, затрудняя её масштабирование.

- Литография и паразитные эффекты металлов: По мере уменьшения размеров узлов становится всё труднее достичь точности в литографии и управлять сопротивлением и ёмкостью в металлических соединениях.

- Физика транзисторов: Природные физические ограничения транзисторов накладывают ограничения на производительность, динамическую мощность и утечки, что делает дальнейшее масштабирование сложным.

Чтобы удовлетворить потребности будущих вычислительных систем, потребуется альтернативное решение для памяти, которое обеспечит высокую производительность на бит, минимизирует энергопотребление и устранит утечки, сохраняя компактные размеры.

По мере того как полупроводниковая индустрия движется к зетаскейл-вычислениям, инновации в архитектуре процессоров, приближении памяти и управлении кэшем становятся ключевыми для решения проблем энергоэффективности. Чиплеты предлагают гибкость и экономию, в то время как 3D-складированная память и архитектуры вычислений в памяти предлагают перспективные решения для устранения узких мест в передаче данных. Однако отрасль должна продолжать искать альтернативы SRAM и другим традиционным технологиям памяти, чтобы сохранять прогресс в условиях проблем масштабирования.

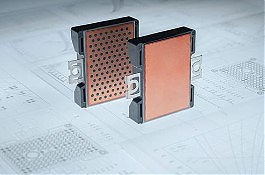

Инновационные решения для памяти: iRAM и STT-MRAM для энергоэффективных SoC

Большие кэши SRAM (L3) значительно улучшают производительность вычислений, повышая число инструкций за цикл, но их высокое энергопотребление создаёт серьёзные проблемы для масштабирования и энергоэффективности. Энергоэффективные альтернативы, такие как магнитная память на основе спинового переноса (STT-MRAM), представляют собой перспективное решение.

STT-MRAM предлагает низкие утечки, работу при низком напряжении и значительную экономию площади. Хотя скорость записи у STT-MRAM ниже, чем у SRAM, последние разработки продемонстрировали время переключения менее наносекунды, что делает её конкурентоспособной для будущих решений памяти.

Новая усовершенствованная технология, интеллектуальная MRAM (iRAM), основанная на STT-MRAM, стала потенциальным прорывом. iRAM предлагает значительные улучшения как в производительности, так и в энергоэффективности, особенно для систем, требующих низкопотребляющей и долговечной памяти.

Ключевые преимущества iRAM:

- Повышенная долговечность: iRAM использует усовершенствованный механизм записи, который минимизирует нагрузку на ячейки памяти, значительно повышая долговечность до уровней, близких к SRAM. Более того, встроенный механизм ремонта в процессе эксплуатации проверяет состояние ячеек MRAM, что ещё больше продлевает срок службы.

- Производительность: Время записи iRAM достигает 30 нс на тестовом чипе 16nm FinFET, с потенциалом для ещё более быстрых записей в зависимости от требований по долговечности. Скорость чтения составляет около 3 нс, что сопоставимо с SRAM, но с гораздо меньшим энергопотреблением как в активном режиме, так и в режиме глубокого сна.

- Надёжность: Спроектированная для работы при низких напряжениях, совместимых с логикой CMOS, iRAM не имеет тока утечки в режиме ожидания и гарантирует сохранность данных более 10 лет при повышенных температурах, обеспечивая надёжную работу для долгосрочных приложений.

iRAM для энергоэффективных приложений IoT и периферийных устройств

Потенциал экономии энергии делает iRAM особенно подходящей для устройств IoT, работающих от батарей, и других периферийных приложений, где критична энергоэффективность.

В качестве примера, приведем следующие:

- Энергопотребление в режиме ожидания и глубокого сна: iRAM потребляет всего 4% энергии в режиме ожидания и лишь 0,02% энергии в режиме глубокого сна по сравнению с традиционной SRAM. Время пробуждения менее 200 нс позволяет быстро получать доступ к данным при сохранении срока службы батареи.

- Плотность и технология: Первые дизайны iRAM демонстрируют вдвое большую плотность по сравнению с SRAM, даже с учётом избыточности для исправления ошибок (ECC), встроенного микроконтроллера для обслуживания и однократно программируемой (OTP) памяти на борту. Быстрое пробуждение поддерживает устройства IoT, которые часто переходят в режим глубокого сна, максимизируя энергоэффективность.

Интерфейсы и шины для гибкой интеграции

Для обеспечения широкой совместимости iRAM поддерживает несколько программируемых шинных интерфейсов, что позволяет легко интегрировать её в SoC на базе чиплетов. Эта гибкость необходима для разработки сложных систем на кристалле (SoC), требующих высокоадаптируемых и энергоэффективных решений для памяти.

Расширение возможностей iRAM с вычислениями в памяти (CIM)

Следующим этапом эволюции iRAM является интеграция функций вычислений в памяти (CIM), что может привести к значительным улучшениям в энергоэффективности ускорителей ИИ. Выполняя вычисления непосредственно в памяти, архитектуры CIM на базе iRAM смогут значительно сократить узкие места передачи данных и снизить энергопотребление.

Это нововведение особенно актуально для приложений периферийных вычислений ИИ, где важна энергоэффективность. Ускоритель на базе CIM с использованием iRAM может обеспечить до 10 раз большую эффективность по сравнению с текущими системами на основе цифровой SRAM. Такой скачок в эффективности позволит iRAM обрабатывать сложные вычисления, такие как задачи инференса ИИ, непосредственно в памяти.

Применение и преимущества CIM-ускорителей на базе iRAM

Интеграция iRAM и CIM в один ускоритель ИИ обеспечит беспрецедентную производительность и энергоэффективность для периферийных приложений.

Эти ускорители будут идеальны для использования в:

- Устройствах IoT.

- Автономных системах.

- Потребительской электронике.

- Цифровой инфраструктуре.

Снижение энергопотребления при сохранении высокой долговечности и скорости обработки данных позволит ускорителям ИИ на базе iRAM обеспечивать эффективную и надёжную обработку данных на периферии.

Комбинация памяти iRAM и ускорителей CIM предлагает передовое решение для следующего поколения SoC. Это нововведение обеспечивает значительную экономию энергии, высокую долговечность и улучшенную сохранность данных благодаря передовым схемотехническим и архитектурным решениям.

По мере того как технологии ИИ и IoT продолжают развиваться, энергоэффективность iRAM в сочетании с её способностью минимизировать энергопотребление делает её краеугольным камнем для создания будущих ускорителей ИИ и периферийных устройств. Используя весь потенциал iRAM и CIM, разработчики SoC смогут удовлетворить строгие требования к энергоэффективности, необходимые для высокопроизводительных и маломощных приложений.

Подписаться на почтовую рассылку / Авторам сотрудничество