Упрощение проектирования SoC с автоматизированным интегрированием аналоговых IP-блоков

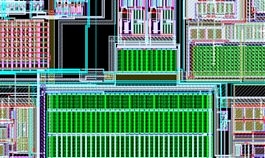

Изменения в практиках проектирования систем на кристалле (SoC) становятся все более заметными с переходом к использованию автоматизированных процессов для интеграции аналоговых IP-блоков вместо традиционного подхода к ручной настройке.

Это направление развития мотивировано стремлением минимизировать задержки в графике проектирования и ускорить весь процесс на несколько месяцев, а также увеличить надежность аналоговых схем за счет снижения их уязвимости к внутричиповым факторам окружающей среды.

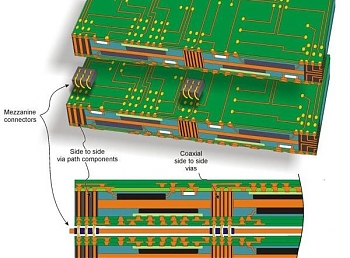

Автоматизация генерации аналоговых IP-блоков предполагает отказ от зависимости от стандартных аналоговых компонентов в пользу процесса, который позволяет интегрировать предварительно разработанные настраиваемые блоки в поток проектирования. Специализированные программные инструменты обеспечивают быструю адаптацию этих блоков для создания подходящих IP-блоков, значительно сокращая необходимое для этого время и усилия.

Масштабируемость аналоговых конструкций при переходе между разными узлами производства микросхем остается значительной проблемой для инженеров в области полупроводников. Переход на более мелкие узлы интегральных схем может быть неэффективным для некоторых аналоговых компонентов. В то же время, несмотря на снижение стоимости цифровой логики в современных SoC, интеграция всех аналоговых функций в экономичной форме продолжает представлять собой вызов.

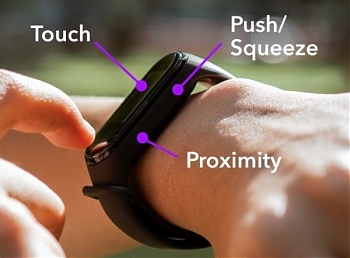

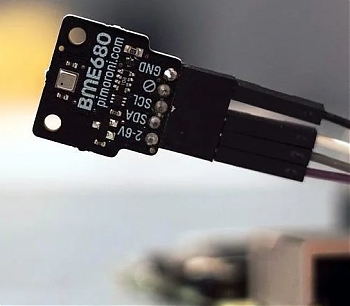

Представитель крупной компании в области разработки полупроводников, занимающийся стратегическим маркетингом IoT, подчеркивает важность выбора технологического процесса при проектировании аналоговых IP-блоков. В этом контексте критически важными становятся такие факторы, как скорость, энергопотребление и стоимость.

Указывается, что стандартные CMOS-дизайны могут подходить для некоторых аналоговых компонентов, но проекты в области IoT зачастую требуют применения специализированных технологических процессов. Такой выбор играет ключевую роль в разработке аналоговых IP-блоков и выделяет сложность взаимодействия между требованиями к дизайну и технологическими возможностями.

В сфере проектирования систем на кристалле (SoC), близкое взаимодействие между поставщиками интеллектуальной собственности (IP) и полупроводниковыми фабриками играет всё более критическую роль. Примером такой динамики служит компания, известная своими фундаментальными аналоговыми компонентами высокой производительности, которая недавно стала частью крупной организации, предоставляющей услуги по проектированию микросхем.

Это сотрудничество началось в начале 2022 года и укрепилось благодаря присоединению к программе IP Alliance ведущей полупроводниковой фабрики, сосредоточив внимание на разработках для процесса на 16 нм с акцентом на тактирование, сенсоры и интерфейсы ввода/вывода.

Компания также расширила свой ассортимент IP-блоков, включив поддержку процесса 12 нм от другого крупного производителя, и объявила о начале работ по разработке аналоговых и смешанных сигнальных IP-блоков для передовых процессов на 4 нм и 3 нм.

Эти стратегические шаги подчеркивают важность сотрудничества между поставщиками IP и фабриками в обеспечении доступности и оптимизации IP для новейших производственных процессов.

Навигация в будущем интеграции аналоговых IP

Автоматизация создания кода для аналоговых IP-блоков является значимым прогрессом в сокращении времени и усилий, затрачиваемых на интеграцию микросхем. Однако этот переход сопровождается вызовами, особенно учитывая, что полупроводниковые фабрики переходят к более мелким и сложным производственным узлам.

Внедрение новейших технологий производства на невиданном ранее темпе приводит к увеличенной сложности и структурным инновациям, как показывает введение технологии FINFLEX на симпозиуме крупного производителя полупроводников.

Переход к более мелким узлам, изначально разработанным для цифровых приложений, требует новаторских подходов от аналоговых дизайнеров. Эволюция технологии производства до технологий gate-all-around представляет уникальные вызовы, такие как компенсация емкости, что требует высокого уровня инноваций при проектировании смешанных сигнальных схем.

Разработка аналоговых и смешанных сигнальных схем для передовых узлов потребует нового поколения инструментальных средств, превосходящих возможности традиционных симуляторов.

Представитель известной компании в области программного обеспечения для электронного проектирования подчеркивает необходимость обновления аналоговых симуляторов для адаптации к последним производственным узлам. Это адаптирование критично для характеризации и оптимизации стандартных библиотек ячеек, которые являются основой для новых чип-дизайнов.

Кроме того, инструменты, предоставляемые поставщиками аналоговых и смешанных сигнальных IP, играют ключевую роль в упрощении и снижении рисков процесса проектирования. Эта поддержка позволяет разработчикам без препятствий интегрировать критически важные IP-блоки в свои проекты SoC, выделяя эволюцию экосистемы поддержки вокруг разработки передовых микросхем.

Подписаться на почтовую рассылку / Авторам сотрудничество