IP-блок новой памяти DDR с инновационной адаптивной технологией

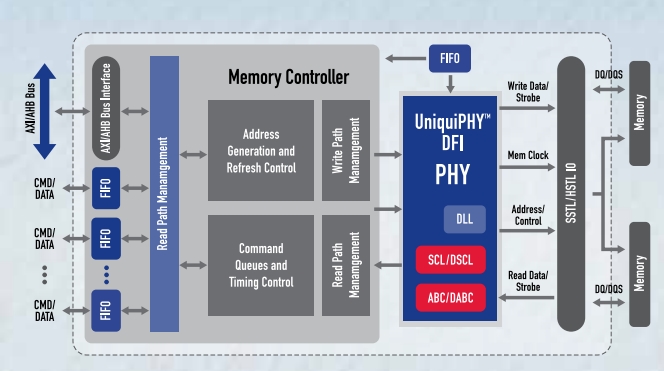

Uniquify сообщила о выдаче нескольким компаниям лицензий на свой новый продукт – IP-блок 28-нм подсистемы памяти DDR4 с максимальной на данный момент для этого типа тактовой частотой 2800 Мбит/с. Обратившиеся компании выбрали новую подсистему памяти благодаря инновационной адаптивной технологии самокалибрующейся логики (SCL) и её динамического варианта (DSCL). Технология позволят калибровать тайминги памяти статически и динамически в реальном времени. Сегмент рынка новой памяти: от широкополосной и сотовой связи до ТВ высокой чёткости, обработки изображений, сетевых систем, испытательных и измерительных устройство, видеооборудования.

В состав современных СнК интегрируется память DDR, работающая на частотах в несколько гигагерц с пикосекундными таймингами в процессах записи/чтения. Проектирование такой памяти под различные виды временных задержек разных систем может привести к неоправданным затратам для настройки во время серийного выпуска.

Технология SCL от Uniquify решает эти проблемы за счёт автоматической калибровки во время подачи питания. Память с данной технологией автоматически подстраивает критические характеристики временных задержек под различные системы и вариации СнК.

Технология DSCL основывается на SCL. При помощи неё калибровка таймингов возможна непосредственно во время работы памяти. Именно благодаря ей 28-нм память DDR4 достигла производительности 2800 Мбит/с, работая в модулях SDRAM с номинальной пропускной способностью 2400 Мбит/с. Во время работы системы температура и напряжение питания изменяются, что негативно влияет на рабочие характеристики памяти DDR и может вызвать сбои её подсистем.

При помощи технологии DSCL критически важные тайминги интерфейса DDR автоматически калибруются в заданные моменты времени, обычно во время низкой активности памяти, чтобы снизить негативное влияние на пропускную способность. Калибровка происходит очень быстро. Для её проведения задействовано мало дополнительных аппаратных средств. Применение DSCL ведёт к уменьшению размеров DDR-трансиверов, поскольку исключается использование других синхронизирующих компонентов (например, блоков FIFO), обычно задействованных в традиционной архитектуре памяти.

Подписаться на почтовую рассылку / Авторам сотрудничество