ARM расширяет линейку ядер для смартфонов и IoT-оборудования

Недавно компания ARM анонсировала новые фирменные ядра, предназначенные для схем смартфонов и оборудования Интернета вещей. Ядро Cortex A-35 обеспечивает поддержкой 64-разрядными операциями мобильные схемы начального уровня, а архитектура ARMv8 Cortex-M позволит реализовать защиту на аппаратной основе в самых компактных 32-разрядных микроконтроллерах при минимальной нагрузке.

Ядро А-35 представляет собой компонент, предназначенный для сегмента смартфонов начального уровня. ARM рассчитывает, что данный сегмент будет расти на 8 % в год и достигнет объёма 1 млрд. устройств к 2020 году. Компания уверенна, что энергоэффективность ядра также привлечёт компонент в широкий диапазон встраиваемых систем, включая абонентские приставки.

Самая компактная конфигурация ядра А-35 с 8 КБ кэша L1 (без L2) умещается на кристалл площадью 0,4 кв. мм., выполненный по 28-нм техпроцессу. Конфигурация потребляет менее 90 мВт на тактовой частоте 1 ГГц и лишь 6 мВт на частоте 100 МГц. Проектировщики могут объединить в кластер до 4 ядер с кэшами L1 и L2, имеющими ёмкость 32 КБ и 1 МБ, соответственно.

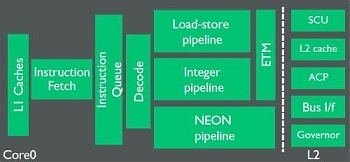

В ядре А-35 задействован 8-каскадный конвейер, способный за 1 такт передавать 2 инструкции между каскадами. Также в ядре реализованы методы предсказания ветвлений, энергоэффективные режимы, улучшения производительности памяти. В геометрии 28 нм ядро А-35 имеет на 25 % более высокую производительность и на 32 % меньшее энергопотребление в сравнении с Cortex A-53 – 64-разрядным ядром среднего сегмента. При обработке 32-разрядного кода на частоте 1,2 ГГц ядро А-35 достигает на 16 % большей производительности и на 10 % меньшего энергопотребления в сравнении с 32-разрядным ядром А-7. Блок вычислений с плавающей запятой (Neon) в 2 раза превосходит по одинарной точности и в 5 раз – по двойной в сравнении с А-7.

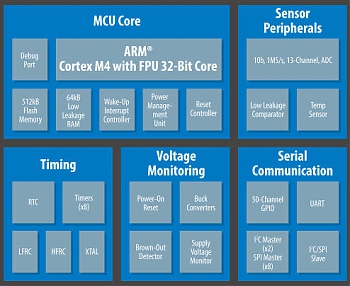

ARM также анонсировала архитектуру для 32-разрядных микроконтроллеров. Архитектура ARMv8-M TrustZone включает дополнительные инструкции, методы обработки исключений и проверки памяти – аппаратные функции, которые реализованы в более дорогих ядрах Cortex-A. Для 32-разрядной версии не требуется гипервизор. Вместо этого применяются механизмы для безопасного переключения между защищёнными и незащищёнными процессами. Дополнительные аппаратные функции по обработке исключений добавят примерно 8 циклов к процессорной обработке прерываний.

Основной профиль архитектуры ARMv8-M реализует дополнительные функции сравнения и ветвления, поддержку защищенного «execute-only» кода и динамическое изменение приоритета прерываний. В профиль добавлены расширения инструкций, опциональный целочисленный DSP-блок, блоки вычисления с плавающей запятой. Это позволит разработчикам создавать защищённые области памяти любого размера посредством указания начального и конечного адресов.

Данный подход позволит чипам выполнять защищённый и незащищённый код параллельно, а также реализовать поддержку безопасных указателей стека.

Подписаться на почтовую рассылку / Авторам сотрудничество