Чип подавителя джиттера синхроимпульсов для схем базовых станций

ADI представила чип подавителя джиттера тактовых сигналов с поддержкой стандарта последовательного интерфейса JESD204B. Компонент найдёт применение в схемах взаимодействия высокоскоростных преобразователей данных с ПЛИС, применяемых в базовых станциях.

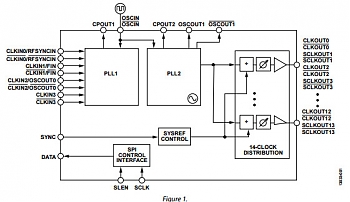

Интерфейс JESD204B разработан для применения в схемах с высокой пропускной способностью. В новом чипе HMC7044 с рабочей частотой 3,2 ГГц реализованы функции для поддержки и улучшения возможностей данного интерфейса. Компонент обладает джиттером 50 фс, что способствует улучшению соотношения сигнал/шум и динамического диапазона высокоскоростных преобразователей. Кроме того, чип предоставляет 14 малошумящих и конфигурируемых выходов, позволяющих реализовать взаимодействие со многими компонентами.

Подавитель джиттера HMC7044 также предлагает широкий ряд функций распределения и управления тактовой синхронизацией. Разработчики базовых станций могут реализовать схему синхронизации на базе всего одного чипа. В схемах базовых станций для множества каналов преобразователей данных последовательного интерфейса JESD204B требуется синхронизация кадров с работой ПЛИС. Новый чип упрощает реализацию подобной схемы за счёт функций генерирования синхронизированных тактовых импульсов (SYSREF).

В чипе реализованы две цепи ФАПЧ, а также встроенный ГУН. Одна цепь ФАПЧ тактирует VCXO-генератор по относительно шумному опорному сигналу, вторая умножает сигнал с VCXO-генератора до частоты ГУН при исключительно-низком добавленном шуме.

При использовании в схемах инфраструктуры сотовых сетей, беспроводных сетях, тактировании преобразователей данных и прочих высокоскоростных цепях связи архитектура чипа HMC7044 обеспечивает отличными рабочими параметрами при низком фазовом шуме. Стоимость компонента стартует с $12,75. Чип выпускается в корпусе LFCSP (10 x 10 мм).

Подписаться на почтовую рассылку / Авторам сотрудничество